ECE 527

SoC Design

Fall 2023

General InformationCourse Syllabus

Lectures

Homework

Machine Problems

Course Project

Exams

Deming Chen (dchen AT illinois.edu)

Office hours: Tuesday 4:00 PM - 5:00 PM Central Time, CSL 250 and Zoom for online students.

https://dchen.ece.illinois.edu/

Zoom link for all Professor and TA Office Hours

Zoom Meeting ID: 830 7092 8177

Passcode: 674838

-Scott Smith(scottcs2 AT illinois.edu)

Office hours: 6:00 PM - 8:30 PM Mondays, Central Time. ECEB 4022 and Zoom for online students (see link above).

-Hanchen Ye (hanchen8 AT illinois.edu)

Office hours: 10:05 AM - 12:30 PM Fridays, Central Time. ECEB 4022 and Zoom for online students (see link above).

4 hours

In-person in ECEB 2013

Time: Tuesday/Thursday 11:00 - 12:20 PM Central Time

Lab details will be introduced in Lecture 3.

The TAs will hold Lab Sessions the week a lab is released. Lab sessions will be run during TA office hours, introduce core lab concepts, and have time for Q&A. More info will be posted to the Campuswire as needed.

Where: 4022 ECE Building and Zoom Meeting (same as office hours link) for online students

When: During TA office hours on the week of the MP release

Lab kits can be picked up from 3-5 PM in CSL 403 on Friday August 25th. One kit per team of two students!

ECE 425 (or equivalent), ECE 391 (or equivalent)

See the syllabus for the link

We encourage you to post your questions on campuswire so everyone can participate in class-related discussions and benefit from them. Please do not include answers or code solutions in public posts and discussions.

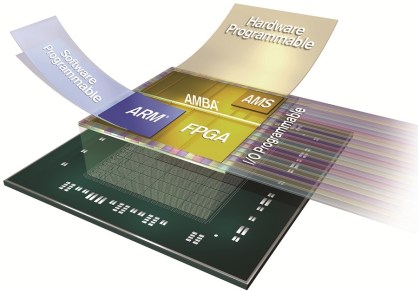

System-on-a-chip (SOC) is an idea of integrating all components of a computer system into a single chip. SOC designs usually consume less power and have a lower cost and higher reliability than the multi-chip systems that they replace. Gartner regards them as the most important type of semiconductor device since the development of the microprocessor. An important enabler for the design of SOCs is the availability of semiconductor intellectual property (IP), which allows a SOC designer to include predefined circuitries, cutting development cycle while increasing product functionality, performance and quality. The implementation of these systems of both hardware and software components and the interaction between hardware and software is an essential part of the design. This course will cover SOC topics on design process, modeling and analysis, design methodology and platform, hardware/software co-design, behavioral synthesis, embedded software, verification, and design space exploration. With a focus on learning of the current SOC design and research topics, students are given opportunities to carry out class projects based on their own interest. Class projects can include software/hardware partitioning, hardware implementation of video compression algorithms, and synthesis for application specific instruction set processors (ASIP). Platform FPGA boards and digital cameras are provided to students to prototype, test, and evaluate their SOC designs.

Machine problem 1: 5% (70% actual work + 30% report)

Machine problem 2: 5% (70% actual work + 30% report)

Machine problem 3: 5% (70% actual work + 30% report)

Machine problem 4: 5% (70% actual work + 30% report)

Machine problem 5: 10% (70% actual work + 30% report)

Class participation: 5%

Homework: 10%

Midterm: 20%

Research Project 35%: (70% actual work + 20% report + 10% presentation)

15% off/day, cannot be more than 3 days late.