ECE 445: Design Document

# ACTIVE CELL BALANCING FOR SOLAR VEHICLE BATTERY PACK

Tara D'Souza, John Han, and Rohan Kamatar TA: Chaitanya Sindagi Team 1

March 5, 2021

## Contents

| 1        | Intr           | roduction                                     | 1  |

|----------|----------------|-----------------------------------------------|----|

|          | 1.1            | Objective                                     | 1  |

|          | 1.2            | Background                                    | 2  |

|          | 1.3            | Visual Aid                                    | 2  |

|          | 1.4            | High-Level Requirements                       | 3  |

| <b>2</b> | Des            | ign                                           | 4  |

|          | 2.1            | Block Diagram                                 | 4  |

|          | 2.2            | Balancing Control                             | 5  |

|          |                | 2.2.1 3.3 V Regulator                         | 6  |

|          |                | 2.2.2 Microcontroller                         | 6  |

|          |                | 2.2.3 Voltage Sense                           | 6  |

|          |                | 2.2.4 Current Sense                           | 7  |

|          |                | 2.2.5 CAN Transceiver                         | 7  |

|          |                | 2.2.6 Software                                | 8  |

|          | 2.3            | Balancing Unit                                | 9  |

|          |                | 2.3.1 Isolated, Bidirectional DC/DC converter | 9  |

|          |                | 2.3.2 Isolated Gate Driver                    | 10 |

|          | 2.4            | Charge Storage                                | 10 |

|          |                | 2.4.1 Supercapacitor $\ldots$                 | 10 |

|          |                | 2.4.2 Precharge                               | 11 |

|          | 2.5            | Battery Management System                     | 11 |

|          | 2.6            | Test Setup Environment                        | 12 |

|          | 2.7            | Battery Modules                               | 12 |

|          | 2.8            | Tolerance Analysis                            | 12 |

| 3        | $\mathbf{Cos}$ | t and Schedule                                | 17 |

|          | 3.1            | Cost                                          | 17 |

|          | 3.2            | Schedule                                      | 18 |

| 4        | $\mathbf{Eth}$ | ics and Safety                                | 19 |

## 1 Introduction

#### 1.1 Objective

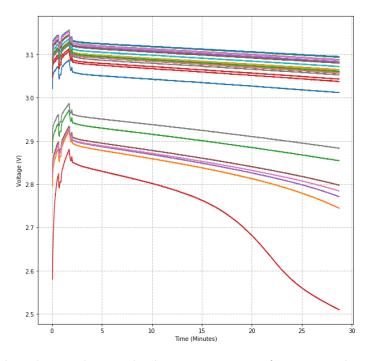

In solar vehicles, charge is collected via a solar array and stored in a battery pack. Illini Solar Car (ISC) utilizes a lithium-ion battery pack with 28 series modules of 15 parallel cells each. The nominal voltage of the battery pack is 100.8 V and the maximum voltage is 117.6 V. In order to ensure safe operation, each battery cell must remain in its safe voltage operating range (2.5-4.2 V). When any single module leaves the safe operating range, the entire pack must stop charging or discharging. During testing and competition, ISC has observed a steady unbalancing of the voltages of the 28 modules. The battery is considered to be unbalanced when the voltages of parallel sets of cells (which we call modules) differ in voltage. As this occurs, the effective capacity of every module in the pack decreases to that of the weakest module. This occurs because once one module reaches 2.5 V, the battery pack can no longer be used even if energy remains in other parts of the pack. In previous competitions, this has rendered as much as 5% state of charge (SoC) unusable. Figure 1 shows how the imbalance in battery modules during the final portion of the race resulted in shutoff of the car while some cells had a significant amount of charge remaining.

To combat this loss in SoC, we propose the addition of an active cell balancing system to ISC's battery pack design. Our system will redistribute charge from modules with more charge to modules with less charge. This design allows for the full capacity of each module in the pack to be utilized to power the car, rather than charge being left unusable in the pack. In this semester, we aim to complete a proof of concept for an active balancing system on a smaller scale that could be extended and integrated into future ISC battery packs.

Figure 1: Module voltages during the last 30 minutes of race. Each color represents a different battery module.

#### 1.2 Background

Solar-vehicle racing is an engineering-based competition where university teams compete to design, build, and race the best car powered only by the sun. These competitions are 2,000 mile endurance races that take place on public roads and highways over the course of many days. The primary goal is to build a reliable car that can maximize efficiency in order to travel the greatest distance during the event.

In order to fully utilize the charge in the battery pack, and travel the greatest possible distance, we believe a custom designed active balancing system to be the best choice. In a passive-balancing system, charge is dissipated from cells with higher voltages such that they are all discharged to the same voltage. Although it is a less complex design, passive balancing does not increase the amount of usable charge in a battery pack as active balancing does.

Additionally, a custom system offers additional benefits that are not available in off-theshelf, active-balancing controllers. In off-the-shelf options such as the LTC3300, charge can only be transferred between neighboring modules [1]. In a custom design, charge could be transferred from any overcharged module to any undercharged module directly. Designs such as the LTC8584 are rated for a low balancing current that would require a parallelized design with multiple chips to reach a reasonable speed for pack balancing. The LTC8584 and other options are also monolithic, meaning an overcharged cell can charge the entire pack, but the pack cannot transfer charge to an undercharged cell [2]. As Figure 1 illustrates, the problem of an under-voltage cell is more relevant to our use case on a solar car. Furthermore, other options such as an EMB1428Q only support up to 60 V for total pack voltage, and the LTC3300 requires an interleaved design to reach higher voltages, which decreases overall balancing efficiency [1],[3]. A custom design could be highly extendable where more balancing units could simply be added to the bus with an extra control signal.

In conclusion, a custom active-balancing system would allow for high-current bidirectional balancing that is scalable to a battery pack of 28 modules.

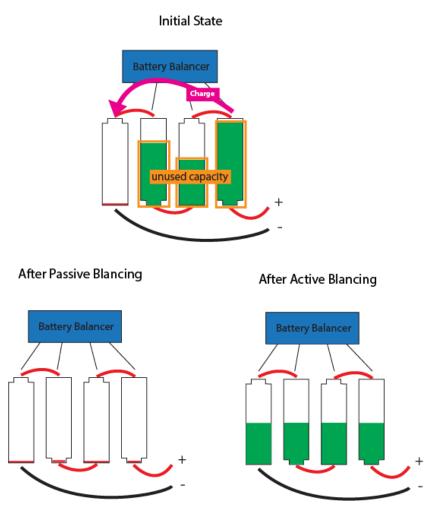

#### 1.3 Visual Aid

Figure 2 shows the motivation and objective for the project. Overall, active-cell balancing moves charge from cells with more charge to cells with less charge to fully utilize the capacity of all modules in the pack. Once the leftmost module is fully discharged, the remaining capacity of the other cells is useless. Manufacturing differences, age, and operating temperature over the cell lifetime can all cause a cell to discharge faster than another. Active balancing rectifies this difference by averaging the capacity of each cell during a charge or discharge cycle so that the entire capacity of the pack is useful. As Figure 2 shows this is advantageous over passive balancing as it does not waste charge.

Figure 2: High-level system objective

#### 1.4 High-Level Requirements

As a first revision in a new custom design, assessing the potential of the design is more important than meeting performance requirements required by a race. These high-level requirements reflect the goals of having a simple proof-of-concept design that future revisions will expand upon. The proof-of-concept design will operate on a pack with four modules in series and each module will have three cells in parallel.

- The active balancing circuit must be able to redistribute energy from the top module to the bottom module with > 50% efficiency.

- Over the course of 30 minutes of balancing, cells above the average pack voltage must see a voltage decrease while cells below the average pack voltage must see a voltage increase.

- Individual module voltages must remain between 2.5 V and 4.2 V for the entire duration of a 30 minute balancing test.

## 2 Design

#### 2.1 Block Diagram

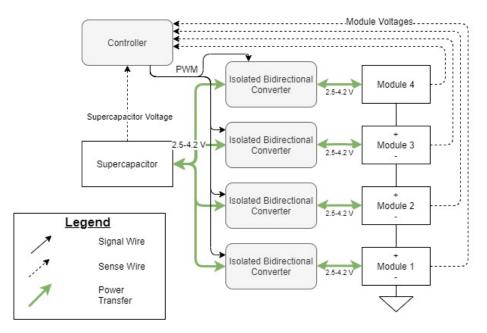

The block diagram for this project is difficult to understand at a technical level without first understanding the high-level intent of the active-balancing architecture we are using. Figure 3 shows the general energy transfer path and the control loop for each DC/DC converter. The intent of this architecture is to transfer energy between each module and the super-capacitor storage element. The controller uses voltage feedback to set the transfer ratio of each converter, which determines if the corresponding module is charging or discharging. Thus, individual modules can be charged and discharged to maintain balance in the pack.

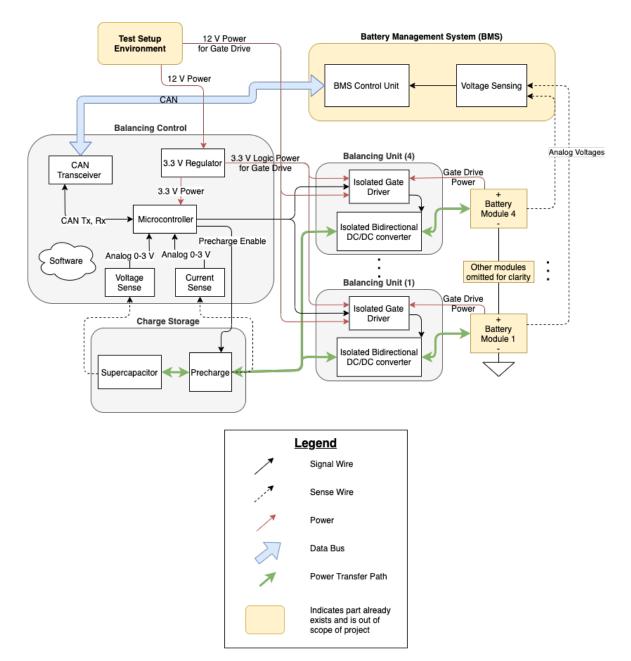

Figure 4 shows the implementation of our intended architecture as a full block diagram. The main energy transfer objective of the design is identical; however, the control and drive of the converters are explained in more detail. The feedback loop for module voltages now goes through existing voltage sensing hardware on the battery management system (BMS) and is transferred to the active balancing microcontroller on a controller area network (CAN) bus. Feedback on the supercapacitor side is measured as an analog voltage by the micro-controller after appropriate resistor divider circuitry. The microcontroller also enables a precharge resistor between the converter and the supercapacitor to limit the initial inrush current on start-up.

Figure 3: High-level architecture of active-balancing system with energy transfer and control loop

Figure 4: Full block diagram of active-balancing design

#### 2.2 Balancing Control

The balancing control system is responsible for driving each of the isolated DC/DC converters to transfer charge either to or from the supercapacitor. The supercapacitor voltage is measured directly from the supercapacitor system as an analog reading, while the module voltages are received from the BMS via CAN. The balancing control then uses the respective voltages to drive each balancing unit using a pulse width modulation (PWM) signal.

#### 2.2.1 3.3 V Regulator

The 3.3 V regulator provides power to the logic elements of the balancing circuit including the microcontroller and gate-drive circuitry. The microcontroller draws on the order of 100 mA during active operation, with a maximum of about 300 mA, and each gate driver draws a maximum of 10 mA from the 3.3 V input. With four gate drivers, and allowing for headroom, the 3.3 V regulator must be able to supply at least 500 mA. None of the components are sensitive to an incorrect supply voltage, so the regulator must be  $3 \pm 0.3$  V of regulation.

| Requirement                             | Verification                          |

|-----------------------------------------|---------------------------------------|

| 1. 3.3 V Regulator must supply          |                                       |

| $3.3 \pm .3$ V from a 12 V input for up | 1. Verify by datasheet specification. |

| to 500 mA of output current.            |                                       |

#### 2.2.2 Microcontroller

The LPC1549 microcontroller controls the balancing unit, measures and controls the super capacitor module, and interfaces with external systems. It interfaces with the BMS via CAN through the CAN transceiver. We chose the LPC1549 because it is used for other systems on ISC and features a CAN interface, analog inputs, digital IO, and state configurable timers (SCT) which are useful for high speed PWM control.

| Requirement                                                                             | Verification                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                         | 1. Program microcontroller to send a CAN mes-<br>sage and blink an LED when receiving a CAN                                                                                                                                                  |

| 1. Microcontroller must transmit<br>and receive messages on CAN bus.                    | message. Connect microcontroller to CAN bus<br>through the CAN transceiver. See that messages<br>are received on the CAN bus and that the LED<br>blinks when messages are sent.                                                              |

| 2. Microcontroller must read analog inputs with accuracy of $\pm$ 10 mV from 0 to 3 V.  | 2. Connect the analog input to a potentiome-<br>ter and measure the voltage of the potentiome-<br>ter with a multimeter. Send measurements via<br>CAN. Verify that measured values are accurate<br>to multimeter reading within $\pm 10$ mV. |

| 3. Microcontroller must generate 4<br>PWM signal with frequency of at<br>least 250 kHz. | 3. Write code to generate 4 PWM signals and<br>probe their outputs with a multimeter. Ver-<br>ify that the signals have defined minimum fre-<br>quency.                                                                                      |

| 4. Microcontroller must generate digital output signals.                                | 4. Write code to blink an LED at 1Hz. Look to see if LED flashes at expected frequency.                                                                                                                                                      |

#### 2.2.3 Voltage Sense

The voltage sense circuit will convert the supercapacitor to a voltage which can be read by the ADC of the microcontroller. It will do this through a resistor divider.

| Requirement                                                                                                                                      | Verification                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Voltage sense must output an analog voltage between 0 and 3 V that can be read as a voltage value with accuracy of $\pm$ 10 mV from 0 to 5 V. | 1. Connect a power supply to the input and configure to output to be several voltages from the range of 0 V to 5 V. Measure output voltage with a multimeter and verify that output range is between 0 V and 3 V and corresponds linearly to input voltage. |

#### 2.2.4 Current Sense

The current sense will create an analog voltage signal to be read by the microcontroller. The voltage across a shunt resistor will be amplified by an op-amp to produce signals that can be interpreted by the microcontroller.

| Requirement                         | Verification                                    |  |  |

|-------------------------------------|-------------------------------------------------|--|--|

|                                     | 1. Connect a power supply across the shunt re-  |  |  |

| 1. Current sense must output an     | sistor. Vary current within specified range and |  |  |

| analog voltage between 0 and 3 V    | measure output voltage signal using voltmeter   |  |  |

| that can be read as a current value | attached between the current sense output pin   |  |  |

| in both directions with accuracy of | and ground. Verify that current value can be    |  |  |

| $\pm$ 50 mA from -10 A to 10 A.     | calculated from voltage within specified accu-  |  |  |

|                                     | racy.                                           |  |  |

#### 2.2.5 CAN Transceiver

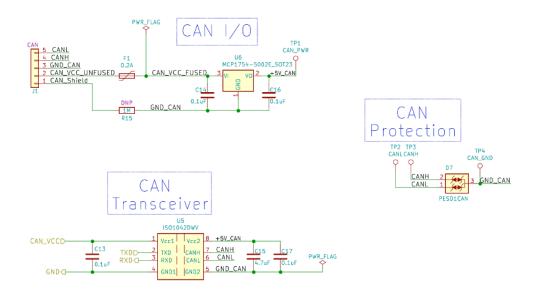

The CAN transceiver is responsible for converting the differential wire pair from the CAN bus to transmit and receive lines that the microcontroller is able to interpret. The CAN transceiver also provides isolation between the board and the CAN bus and converts the 3.3 V board logic to 5 V CAN logic. If the CAN transceiver works correctly, the microcontroller should be able to send and receive messages from a connected CAN bus. See Figure 5 for a complete CAN schematic.

| Requirements                                                                                                | Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. CAN transceiver must relay mes-<br>sages on the CAN bus in a readable<br>format for the microcontroller. | <ul> <li>1.1. Program microcontroller to send heartbeat message via CAN once every second. Attach a CAN bus analyzer to the CAN bus and use it to provide CAN power. Read CAN messages in software to determine if heartbeat message is sent from the balancing microcontroller.</li> <li>1.2. Program microcontroller to blink an LED on the receipt of a certain CAN message. Connect the CAN bus analyzer and supply CAN power. Send designated message using CAN bus analyzer and confirm that an LED blinks on the board.</li> </ul> |

Figure 5: Detailed schematic of CAN transceiver, input and output, and protection

#### 2.2.6 Software

The primary purpose of the software in this system is to control the individual balancing units through PWM control of a number of MOSFET gates in the balancing unit and in the precharge circuit. This requires voltage and current inputs to achieve closed loop control. The software must decide where to move charge. It will do this by determining which module has the least charge and which has the most charge based on their voltage readings. The software then must generate PWM signals to charge the supercapacitor and enable precharging when necessary based on voltage inputs. It will then generate PWM signals to transfer the supercapacitor charge to the low voltage module. In addition to these functions, the software will send log messages over CAN for diagnostics and performance analysis.

| Requirement                                                                                                                                                                                                         | Verification                                                                                                                                                                                                                |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1. The software must enable                                                                                                                                                                                         | 1. Vary the voltage inputs and measure the                                                                                                                                                                                  |  |  |

| precharging upon startup such that                                                                                                                                                                                  | precharge enable. Verify that precharge is enabled                                                                                                                                                                          |  |  |

| the current never exceeds 10 A.                                                                                                                                                                                     | while the capacitor is uncharged.                                                                                                                                                                                           |  |  |

| 2. The software must disable all isolated gate drivers when in safe state.                                                                                                                                          | 2. Connect a power supply configured to output 4.3 V in place of one module. Verify that the enable digital output from the microcontroller is enabled.                                                                     |  |  |

| 3. The software must be able to<br>identify modules above and below<br>pack average and generate PWM<br>signals to drive the redistribution<br>of charge such that the identified<br>modules approach pack average. | 3. Provide voltage readings such that one module<br>is above average and one is bellow average. With<br>an oscilloscope probe the output signals. Verify<br>that PWM signals are generated for the high and<br>low modules. |  |  |

### 2.3 Balancing Unit

There is one balancing unit per module. The function of the balancing unit is to transfer energy in either direction across the converter between the supercapacitor bus and battery module. The PWM control responsible for setting the conversion from module to bus is received from the balancing control.

#### 2.3.1 Isolated, Bidirectional DC/DC converter

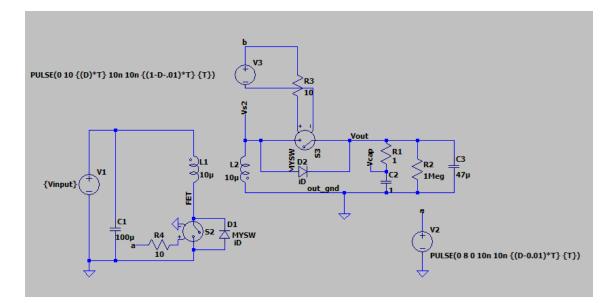

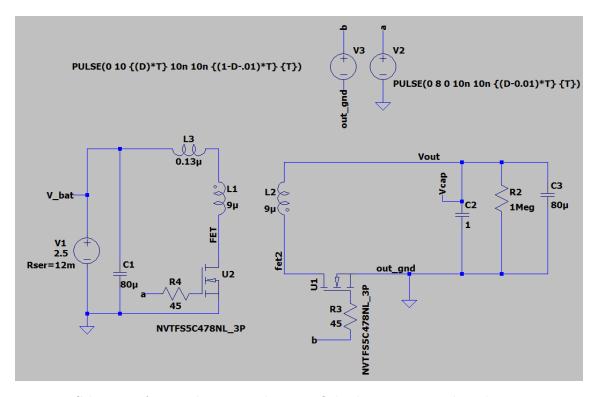

The DC/DC converter implements an isolated flyback topology with synchronous switching. The secondary side voltage will be between 2.5 V and 4.2 V. The primary voltage will be nominally set at the pack average voltage. See Figure 6 for a schematic implementation used for simulation.

| Requirement                                                                       | Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Converter must be able to<br>sink or source at least 3 A of                    | 1.1. Connect a power supply at 3 V to the super-<br>capacitor side of the converter and a 1 $\Omega$ power<br>resistor to the module side. Attach a function<br>generator set to a 250 kHz 0-3.3 V PWM wave to<br>the gate drive circuit. Also connect a Yokogawa<br>power meter to measure output voltage and current<br>into the load resistor.                                                                                                                       |

| current on the secondary side.                                                    | 1.2. Ramp up the duty cycle of PWM signal<br>and measure output RMS voltage and current on<br>the load using a Yokogawa power meter. Ensure<br>that RMS output current reaches 3 A on the load<br>and the converter remains functional at this current<br>draw for at least 1 minute.                                                                                                                                                                                   |

| 2. Converter must have an ad-<br>justable input and output range<br>of 2.5-4.2 V. | <ul> <li>2.1. Set input supply to 4.2 V, adjust duty cycle until the output voltage is 2.5 V.</li> <li>2.2. While changing the PWM duty cycle on the function generator to keep output voltage at 2.5 V, lower the input voltage to 2.5 V.</li> <li>2.3. Keep the supply voltage constant and adjust duty cycle until the output voltage is 4.2 V.</li> <li>2.4. Increase the supply voltage to 4.2 V while using the duty cycle to maintain a 4.2 V output.</li> </ul> |

| 3. Converter must be capable of bidirectional power transfer.                     | 3. Turn off the supply move the power supply to the module side of the transformer and the load resistor to the secondary side. Repeat the above verifications with input and output reversed.                                                                                                                                                                                                                                                                          |

Figure 6: Schematic for simulating synchronous flyback converter using ideal switches and diodes

#### 2.3.2 Isolated Gate Driver

The isolated gate driver is required for the balancing unit because the each battery module is isolated from the control logic and the gate drives for a power MOSFET require large currents, which cannot be supplied from a microcontroller. The primary-side gate drive is powered from the 12 V external supply while the secondary-side gate drive is powered from a battery module. To minimize the number of signals from the microcontroller, the isolated gate driver IC should also implement inversion and deadtime.

| Requirements                                                                                                                                          | Verification                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1. Gate driver must transfer a logic side PWM to the primary drive pin output and an inverted signal with deadtime to the secondary drive pin output. | 1. To confirm that a PWM input is transferred to<br>the output and inverted, supply logic power at 3.3 V<br>, and power each gate drive at 3.5 V using a power<br>supply. Apply a PWM input to the logic side and<br>probe the voltage on each gate drive pin using a dif-<br>ferential oscilloscope probe. Ensure that the duty<br>cycle for the input and primary-output are the same<br>and that the secondary-side drive is inverted. |  |  |

#### 2.4 Charge Storage

The function of this subsystem is to store charge from the modules of higher voltage to be redistributed back to the modules of lower voltage.

#### 2.4.1 Supercapacitor

The supercapacitor will store and release charge to enable the redistribution of charge between any sets of modules. The supercapacitor will also regulate the voltage on the shared primary power bus.

| Requirements                      | Verification                                    |  |  |

|-----------------------------------|-------------------------------------------------|--|--|

| 1. Supercapacitor must operate up | 1. Verify on the datasheet that the supercapac- |  |  |

| to 4.5 V.                         | itor is rated for more than 5 V.                |  |  |

#### 2.4.2 Precharge

On start-up, the supercapacitor can be susceptible to initial current spikes which can damage the system components. While it is possible to limit the current inrush using the control loop, a simple hardware solution is to use a precharge circuit. This circuit will consist of a power resistor that is temporarily connected in series with the supercapacitor to limit the inrush current upon startup. Once the circuit voltage steadies, the power resistor will be disconnected and the precharging will be complete.

| Requirements                                                                                                                     | Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1. Precharge circuit must limit in-<br>rush current to at most 10 A. Be-<br>yond which the transformer is likely<br>to saturate. | 1.1. Connect a power supply to the input of the precharge circuit and the supercapacitor to the output. Set up current measurement using an oscilloscope on the supercapacitor power supply input leads. Ensure that the supply current limit is at least 10 A.                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                  | 1.2. Step up the supply voltage to 4.2 A. Confirm that current on input does not exceed 10 A as measured on the oscilloscope.                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2. Precharge resistor must be able<br>to dissipate 42 W of power for at<br>least 1 s.                                            | <ul> <li>2.1. Attach precharge resistor across power supply. Set voltage on power supply such that 42 W of power will be dissipated across the resistor (the exact value changes if a higher value resistor is used). Turn on the power supply and turn off output after at least 1 s.</li> <li>2.2 Probe the terminals of the resistor using a digital multimeter to measure resistance. Confirm the resistance is within 10 % of the rated value, thus the resistor can dissipate the needed power over a 1 s time frame.</li> </ul> |  |

## 2.5 Battery Management System

The Battery Management System (BMS) queries all peripheral hardware to ensure that the batteries are operating within specifications outlined in the datasheet. This includes voltage, temperature, and current sensing within the car. In the event that unsafe operation is detected, the BMS will isolate the batteries from the load and disable any balancing from occurring. The BMS is out of scope for our project but it will be used to monitor cell voltages and to send that data to the Balancing Control PCB via CAN.

#### 2.6 Test Setup Environment

The Test Setup is out of scope of this project but will be used to supply 12 V power to the Balancing Control PCB and 12 V power to the isolated gate drivers.

#### 2.7 Battery Modules

The battery modules are out of the scope of this project. We will be using four modules in series of 3 parallel cells each to conduct testing and verification of our proof-of-concept design. These cells will be 18650 lithium-ion battery cells.

#### 2.8 Tolerance Analysis

The essential feature of our design is a bidirectional flyback converter. A bidirectional converter is one of the unique advantages of our custom architecture in that it will allow any module to charge or discharge into any other module. The bidirectional flyback topology is shown with ideal components in Figure 6. There are three main requirements for the flyback converter: 1) It must have a 2.5 to 4.2 V adjustable input range and a 2.5 to 4.2 V adjustable output range. 2) The converter must be able to handle at least 3 A of current input or output. 3) The converter must be capable of bidirectional operation. It is critical that even including tolerances the flyback convert module meets the requirements.

The primary components in the flyback converter are the transformer, the primary-side switch, and the secondary-side switch. To ensure proper operation of the flyback converter, we performed simulations using the worst-case tolerances for each of these real components. The PA6605-AL from CoilCraft is an off-the-shelf transformer that is rated for 12 V and 60 W with a saturation current of 12.5 A. The nonidealities of the transformer are its leakage inductance, copper losses, and core losses. The CoilCraft transformer has a maximum total leakage inductance of 0.13  $\mu$ H and a maximum DC resistance of 4.7 m $\Omega$  per winding. No core losses are specified in the datasheet, so we will use the simplified model that ignores core losses. The transformer also has a magnetizing inductance of at least 9  $\mu$ H referred to the primary. This inductance is utilized as part of the converter energy transfer process, so a large magnetizing inductance is ideal [4].

The synchronous flyback design requires active switches on both the primary and secondary side of the transformer. The selected MOSFET, an ON Semi NVTFS5C478NL, is rated for 40 V and 26 A. It also has a gate charge of 2 nC and a maximum  $R_{ds}$ , on of 45 m $\Omega$ [5]. The last tolerance to consider is the derating and equivalent series resistance of the two filtering capacitors on the input and output. The chosen capacitors are 100 uF, with an ESR of 74 m $\Omega$  and a tolerance of 20%. Thus, in a worst-case each capacitor is only 80  $\mu$ F instead of its desired 100 uF The goal is to show that within these specifications, the converter can still operate at maximum power without exceeding the transformer saturation limit of 12.5 A or the switch blocking limit of 40 V. Operation was simulated in two scenarios worst-case scenarios: 1) The supercapacitor at 4.2 V is charging an undercharged module at 2.5 V. 2) A 4.2 V module is charging the supercapacitor at 2.5 V. In both simulation cases, the current was set to approximately 3 A by changing the duty cycle.

Mathematical derivations of the flyback operation become unrealistically complex when

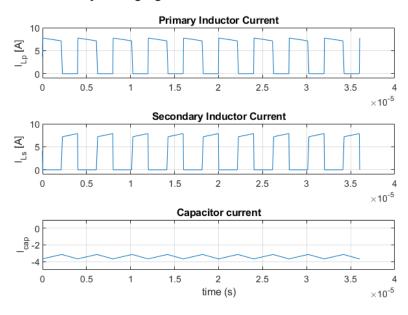

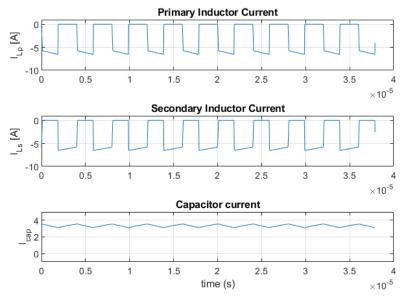

accounting for all real components, so we verified operation using LTSpice simulation software. Figure 7 simulates the operation of the circuit using a real inductor model and ideal switches. The results from this figure show that without considering the real switches and capacitors, the transformer tolerance will still yield a product well within required specifications.

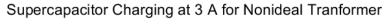

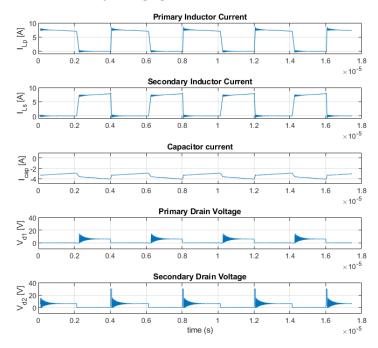

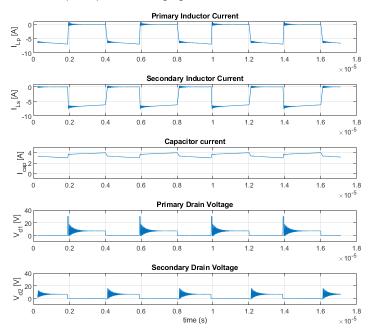

Next, the real switches and capacitors were included in the simulation. Figure 8 shows the complete converter simulation with worst-case tolerances. The simulation results for full-current charge and discharge is shown in Figure 9. The results of the simulation show that, the inductor currents do not exceed saturation limits. The peak inductor current was approximately 8.5A, and the rms current was 3.4 A in both simulations. Furthermore, the maximum gate voltage due to ringing is 30 V, which does not exceed the MOSFET rating of 40 V. Thus, the converter can still operate within specifications given worst-case tolerances.

In the process of this analysis, we gained additional insight into the large ringing a flyback topology induces on the MOSFET drains. In further analysis we plan to analyze snubber options to reduce this ringing including a resistor-capacitor-diode clamp circuit, or a zener clamp circuit.

Battery Charging at 3 A for Nonideal Tranformer

(a) A 4.2 V supercapacitor charging a 2.5 V battery at approximately 3 A

(b) A supercapacitor at 2.5 V discharges a 4.2 V modules at approximately 3 A

Figure 7: Simulation results of for peak inductor current and capacitor charging current for a non-ideal transformer

Figure 8: Schematic for simulating synchronous flyback converter with real components at worst-case tolerances. Note: series resistances are not shown because they are set within the properties of each component

Battery Charging at 3 A in Non-ideal Circuit

(a) A 4.2 V supercapacitor charging a 2.5 V battery at approximately 3 A

Supercapacitor Charging at 3 A in Non-ideal Circuit

(b) A supercapacitor at 2.5 V discharges a 4.2 V module at approximately 3 A

Figure 9: Simulation results of for peak inductor current, capacitor charging current, and drain blocking voltage for a non-ideal circuit

## 3 Cost and Schedule

#### 3.1 Cost

We estimate 20 hours of work per week for 3 people over 15 weeks at \$ 50 per hour. With 2.5 times overhead, we estimate a total development cost of \$ 112,500 for this proof-of-concept design.

To build the devices we estimate a total cost of \$ 230.19 with the cost breakdown shown in Table 1. Note that the components shown in the cost breakdown are derived on current preliminary part selection and are subject to change.

| Part                       | Part Number     | Unit Price | Quantity   | Total     |

|----------------------------|-----------------|------------|------------|-----------|

| Microcontroller            | LPC1549         | \$ 9.62    | 1          | \$ 9.62   |

| 3 V Regulator              | R-783.3-1.0     | \$ 7.08    | 1          | \$ 7.08   |

| CAN Transceiver            | ISO1042DWVR     | \$ 3.94    | 1          | \$ 3.94   |

| Supercapacitor             | DGH255Q5R5      | \$ 3.05    | 1          | \$ 3.05   |

| Isolated Gate Driver IC    | Si8274          | \$ 2.40    | 4          | \$ 9.60   |

| Transformer                | PA6605-AL       | \$ 16.95   | 4          | \$ 67.80  |

| Power MOSFET               | NVTFS5C478NL    | \$ 1.00    | 8          | \$ 8.00   |

| Electrolytic Capacitors    | DGH255Q5R5      | \$ 3.05    | 2          | \$ 6.10   |

| Lithium-Ion Battery        | 18650 GA        | \$ 5.00    | 12         | \$ 60.00  |

| Various Passive Components | n/a             | \$ 0.10    | 100        | \$ 10.00  |

| Connectors                 | Molex KK series | \$ 1.00    | 15         | \$ 15.00  |

| PCB Manufacture            | n/a             | \$ 30.00   | 1          | \$ 30.00  |

|                            | •               | •          | Total Cost | \$ 230.19 |

| Table 1: | Cost | breakdown   | of re | equired | components  |

|----------|------|-------------|-------|---------|-------------|

| TODIO I. | 0000 | DICULTUOWII | OI IC | quitou  | componentos |

In total, development and component costs sum to an overall project cost of \$ 112,730.19.

## 3.2 Schedule

Our project schedule is broken down by group member as follows.

| Week | Tara D'Souza                                                                            | John Han                                                                                       | Rohan Kamatar                                                                        |

|------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 3/8  | Design balancing control<br>schematic                                                   | Create high-level design<br>for software to generate<br>PWM signals for balanc-<br>ing control | Design balancing unit<br>schematic                                                   |

| 3/15 | Design balancing control<br>PCB layout                                                  | Spot weld batteries into<br>modules for testing, cycle<br>battery modules                      | Design balancing unit<br>PCB layout                                                  |

| 3/22 | Finalize and order PCB components                                                       | Program PWM control                                                                            | Program PWM control                                                                  |

| 3/29 | Conduct basic testing for<br>balancing control PCB ,<br>make appropriate revi-<br>sions | Assist with PCB assembly and testing                                                           | Conduct basic testing<br>for balancing unit PCB,<br>make appropriate revi-<br>sions  |

| 4/5  | Complete second revision<br>of balancing control PCB<br>and send for manufactur-<br>ing | Program Balancing algo-<br>rithm and additional di-<br>agnostics                               | Complete second revision<br>of balancing unit PCB<br>and send for manufactur-<br>ing |

| 4/12 | Perform complete assem-<br>bly and hardware testing<br>of balancing control PCB         | Perform full system test-<br>ing with software                                                 | Perform complete assem-<br>bly and hardware testing<br>of balancing unit PCB         |

| 4/19 | Conduct full system test-<br>ing                                                        | Conduct full system test-<br>ing                                                               | Conduct full system test-<br>ing                                                     |

| 4/26 | Final Demonstration                                                                     | Final Demonstration                                                                            | Final Demonstration                                                                  |

| 5/3  | Final Paper                                                                             | Final Paper                                                                                    | Final Presentation                                                                   |

Table 2: Schedule overview of all project team members broken down by week

## 4 Ethics and Safety

This project will deal with two significant dangers: high-voltage electronics and lithiumion batteries. High-voltage electronics pose a danger of electric shock. At higher voltages greater current can flow through the body, delivering more power and therefore an increased risk of injury and death [6]. We will minimize this risk by utilizing the one hand technique and always utilizing proper tools and safety equipment.

Lithium-ion batteries pose a significant risk due to their high energy density and instability. In a 5 year period over 25,000 overheating and fire incidents involving lithium ion batteries were reported. However, this risk is only significant when the batteries are damaged or utilized outside of their specified operating conditions [7]. The safe operation of lithium-ion batteries is well defined by the American Solar Challenge regulations [8] under which ISC designs its vehicles. These regulations require active protection of overvoltage, undervoltage, over current and over temperature where active protection means that the system will shut off automatically in any of the above fault conditions. The team will implement these systems and verify them before relying on them to provide protection.

While working with these dangers it is also important to minimize danger and risk to the public. The IEEE Code of Ethics states that it is our responsibility "to hold paramount the safety, health, and welfare of the public" [9]. We will ensure this through safe storage of our batteries, isolation of high voltage, and clear labeling of enclosures to protect the public from the dangers of our project. Our batteries will be stored in a fire cabinet while not in use and will always be stored at safe charge levels. Additionally, the battery pack will only be operated under supervision of our team members.

Should an accident occur during assembly or otherwise, the team will follow Division of Research Safety guidelines [10]. This includes always being prepared with proper safety equipment such as fire extinguishers and sand. The risk of thermal runaway of damaged batteries can also be mitigated through discharge in a saltwater solution. If a battery is damaged we will follow DRS procedures for disposal by placing the battery in a saltwater solution to discharge and contacting the DRS for proper disposal.

While high voltage batteries can be dangerous, with proper procedures and design, these risks can be mitigated which will allow us to create a safe and functional system.

## References

- Analog Devices, "High Efficiency Bidirectional Multicell Battery Balancer," LTC3300-1 datasheet, Jun. 2019.

- [2] Linear Technology, "2.5A Monolithic Active Cell Balancer with Telemetry Interface," LT8584 datasheet, 2013.

- [3] Texas Instruments, "Switch Matrix Gate Driver," EMB1428Q datasheet, May 2012 [Revised May 2013].

- [4] Coilcraft, "Planar Transformer," PA6605-AL datasheet, May 2018.

- [5] Division of Research Safety, "Electrical Safety In The Research Laboratory," Division of Research Safety Library [Online]. Available: https://drs.illinois.edu/Page/ SafetyLibrary/ElectricalSafetyInTheResearchLaboratory [Accessed: Feb. 16th, 2021].

- [6] ON Semiconductor, "MOSFET Power, Single N-Channel," NVTFS5C478NL datasheet, Sept. 2019.

- [7] Occupational Safety and Health Administration, "Preventing Fire and/or Explosion Injury from Small and Wearable Lithium Battery Powered Devices," Safety and Health Information Bulletins [Online]. Available: https://www.osha.gov/dts/shib/ shib011819.html [Accessed: Feb. 16th, 2021].

- [8] Innovators Educational Foundation, "American Solar Challenge 2021 Regulations," Release A [Online]. Available: https://www.americansolarchallenge.org/ASC/wpcontent/uploads/2020/10/ASC2021-Regs-EXTERNAL-RELEASE-A.pdf [Accessed: Feb 16th, 2021].

- [9] IEEE.org, "IEEE Code of Ethics," IEEE Policies [Online]. Available: https://www.ieee.org/ about/corporate/governance/p7-8.html [Accessed: Feb 16th, 2021].

- [10] Division of Research Safety, "Battery Safety," Division of Research Safety Library [Online]". Available: https://drs.illinois.edu/Page/SafetyLibrary/BatterySafety [Accessed: Feb. 16th, 2021].