## ECE-483 Instructions Calculating Total Harmonic Distortion

Here is a brief description on how to take FFT and calculate THD in cadence.

- Virtuoso® Analog Design Environment L Editing: ece483\_demo Tb\_THD schematic N. \_ \_ × Launch Eile Edit View Create Check Options Migrate Window NCSU Help cādence | 🗅 🗁 🗃 🖶 || 🚸 🗘 🖾 🗙 🕦 T⁄ 🖻 🤌 🥐 🎊 - Tˆ T´ || 🍳 🔍 🍳 🕅 || 🏞 ጊ ጊ 🛎 🛥 🖻 🗖 🖫 💁 🐼 🦓 🎠 🕀 🎝 🔍 🔍 🔾 🔹 💭 🔹 🕜 🚱 🛛 Workspace: ADE L - -| 🎇 🖽 🖾 🕥 🕥 🔟 | 🗐 🗏 {= | 1🔍 • 🕼 • 🐉 • Edit Object Properties Navigator ? 🗗 🗙 Cell Name vsource off 🍸 Default - ... -View Name symbol off a off -Instance Name ¥2 Th THD 🖷 V2 (vs Add Delete Modify l\_ gnd User Property Master Value Local Value Display lvslgnore TRUE off -CDE Parameter Value Display DC voltage 0 V off sine 🔽 Source type off -• Property Editor ? 🗗 🗙 Frequency name 1 off 🗐 instance 🤜 All -Frequency 1 1M Hz • off true 0 V sine • 300.0m ¥ Amplitude 1 (Vpk) off DC voltage • Phase for Sinusoid 1 off • Freque... 1M Hz Amplitu... 300.0m Sine DC level 900m ¥ off OK Cancel Apply Defaults Previous Next Help Phase f... Sine D... 900m V Delay ti false lav sei

- 1. I used the following ideal input sine wave for which I want to calculate THD.

- 2. To improve the accuracy of my transient simulation I run it for atleast 10 cycles of my input (10 usec) in convestavtive mode. To improve the simulation accuracy even further change the abstol and reltol options on your simulator as shown below.

- 3. Here I changed the abstol to 1e-7 and reltol to 1e-4 by making it even smaller you can improve your simulation accuracy. But the reltol at least 100X larger than abstol.

| 📱 Virtuoso® Analog Design Env                                                             |                                                                                                                                         | Simulator Options x                                            |                                                            |                                        |                                                            |        |              |             |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|------------------------------------------------------------|--------|--------------|-------------|

| Launch S <u>e</u> ssion Set <u>up A</u> nalyses <u>V</u> aria                             | iables <u>O</u> utputs <u>Simulation</u> <u>R</u> esults <u>T</u> ools                                                                  | Help cādence                                                   | Ma                                                         | ain Algoriti                           | nm Component                                               | Check  | Annotation   | Miscellaneo |

| Design Variables Name Value                                                               | Analyses<br>Type Er<br>I tran C Molece Checking<br>MDL Control<br>Reliability<br>Options<br>Netlist<br>Output Log<br>Convergence Aids > | ents<br>Analog<br>Digital<br>Mixed Signal<br>Save Save Options | relto<br>resi<br>vab<br>iabs<br>TE<br>temp<br>tnon<br>temp | dualtoi<br>stoi<br>toi<br>MPERATURE OF | 1e-4<br>1e-12<br>TIONS<br>27<br>27<br>27<br>27<br>27<br>27 |        |              |             |

| > Results in /home/mandwa2/cadence/sir Plot after simulation: Auto Plotting mode: Replace |                                                                                                                                         |                                                                |                                                            |                                        |                                                            | OK Can | cel Defaults | Apply Help  |

| mouse L:<br>3(4) Analog                                                                   | M:<br>Status: Ready                                                                                                                     | R:<br>  T=27 C   Simulator: spectre                            |                                                            |                                        |                                                            |        |              |             |

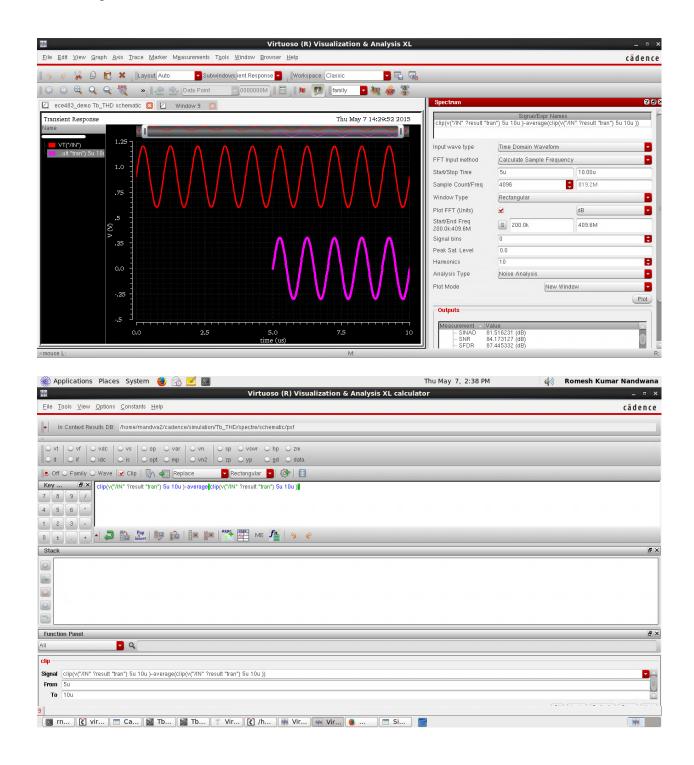

4. Since the transient output waveform has the DC component in it and also might have some initial settling errors, so first I removed the initial 5us of the timing waveform using "clip" function from the calculator. Then the DC component is removed by substracting the average of the waveform. The two waveforms looks like the following. The clipped and averaged waveform is centered around zero.

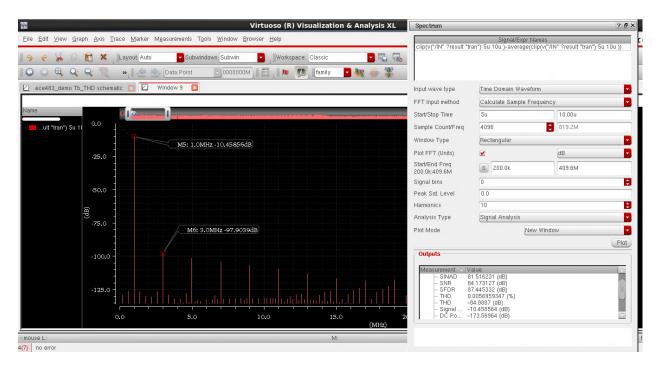

5. Then use the spectrum window as shown in the following to generate your spectrum plot. THD in this case is calculated as -84dB with first harmonic power as -10dB and third harmonic as -97dB.

## Helpful Link

Open the following link in a web browser on EWS machine or in your fastx.

file:///software/cadence-Dec2013/IC616/doc/vivaxlug/aapJ.html #1205661

You can open this link only on the EWS machines. It properly explains the method with screen shots.