## ECE190 Exam 1, Fall 2008 Thursday 25 September

| Name: |  |  |  |

|-------|--|--|--|

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

|       |  |  |  |

- Be sure that your exam booklet has 9 pages.

- The exam is meant to be taken apart!

- Write your name at the top of each page.

- This is a closed book exam.

- You may not use a calculator.

- You are allowed one  $8.5 \times 11$ " sheet of handwritten notes.

- Absolutely no interaction between students is allowed.

- Challenging problems are marked with \*\*\*.

- Show all of your work.

- Don't panic, and good luck!

"...there would be no more wars, the nations were so economically interdependent."

—S. Foster Damon, remembrance ca. 1912

| Problem 1 | 20 points  | - |

|-----------|------------|---|

| Problem 2 | 20 points  |   |

| Problem 3 | 10 points  |   |

| Problem 4 | 25 points  |   |

| Problem 5 | 25 points  |   |

| Total     | 100 points |   |

| Name:                                                               |                          |          |        |                |          |          |          |              |              |       |            |       |          |         | _      |          | 2                  |

|---------------------------------------------------------------------|--------------------------|----------|--------|----------------|----------|----------|----------|--------------|--------------|-------|------------|-------|----------|---------|--------|----------|--------------------|

| Problem 1 (2                                                        | 20 points                | ): Sho   | ort A  | nsv            | vers     | <b>,</b> |          |              |              |       |            |       |          |         |        |          |                    |

| Please answer c<br>answer is proba                                  |                          |          | find y | our.           | self     | writ     | ing 1    | more         | e tha        | an a  | few        | WOI   | rds or a | a simp  | le dra | wing, y  | your               |

| Part A (5 poi<br>generates an ove                                   |                          |          |        |                |          | olem     | ent      | data         | ı typ        | oe, v | vhat       | is t  | he sm    | allest  | positi | ve nun   | nber that          |

| Part B (5 points) Part C (5 points) address outside stored in R5. W | nts): Using<br>the range | g one or | · more | e LC           | C-3 i    | nstru    | uctio    | ons,<br>ssun | imp<br>ne th | lemo  | ent a      | ı bra | unch if  | positiv | ve (BI | Rp) to a | an<br>branch is    |

| Address                                                             | Instruc                  | rtion    |        |                |          |          |          |              |              |       |            |       |          |         |        |          |                    |

| x3000:                                                              | mstruc                   | 1        | 1      | 7              | - I      | T        | 1        |              | F            | T     | 1          |       |          |         |        |          |                    |

|                                                                     |                          | r        | 3      | 1              | T.       | T.       | a        | 1            |              | 1     | a.         | j     |          |         |        |          |                    |

| x3001:                                                              | 1 1                      | 8        | 1      | N.             | B        | I        | Ţ        | N.           | - I          | 1     | Ţ          | N.    | 18       |         |        |          |                    |

| 2002                                                                |                          |          | -1     | 1              | - 12     | <u> </u> | 9        |              | - 1          | 1     | 3          | 3     |          |         |        |          |                    |

| x3002:                                                              | 9 9                      | 18       | - SS   | /31<br>33      | 18<br>18 | *        | 55<br>Se | 推            | 18           | T.    | 100<br>200 | 器     |          |         |        |          |                    |

| x3003:                                                              |                          |          | -1     |                |          | -        | j.       | 1            |              | -1    | 1          | Į.    |          |         |        |          |                    |

| A3003.                                                              |                          | r l      | 3      | i              | 1        | ī        | 9        | j            | ı            | 1     | 9          | ì     |          |         |        |          |                    |

| Part D (5 point the memory byth the instructions  MAR               | e-addressa               | ible (a  | byte i | s 8 1<br>its w | bits)    | witl     | nout     | cha          | ngii         | ng it | s siz      | e, a  | nd witl  | nout cl | hangir | were t   | to make<br>size of |

Name: \_\_\_\_\_

#### Problem 2 (20 points): Logic Circuits

**Part A** (3 points): Using exactly one logic gate whose inputs are not inverted, draw a logically equivalent circuit to the one pictured below.

3

**Part B** (3 points): Using exactly one logic gate whose inputs are not inverted, draw a logically equivalent circuit to the one pictured below.

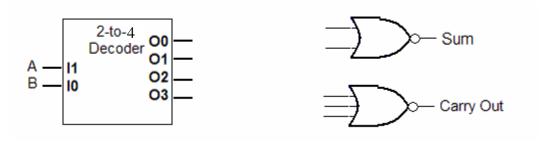

**Part C** (6 points): Draw the necessary connections to implement a half-adder (an adder without a carry input) using the 2-to-1 decoder and the two NOR gates pictured below.

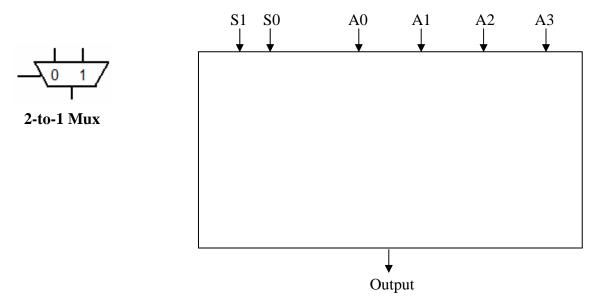

**Part D** (8 points): Using three 2-to-1 multiplexers (shown to the left below), draw a circuit which performs the function of a 4-to-1 multiplexer with inputs: A0, A1, A2, A3, and select bits: S1, S0.

Name:

#### **Problem 3** (10 points): Memory

In a typical memory, setting the write enable input (WE) to 1 causes all bits of the selected memory location to accept new values. For a certain ECE445 (senior design) project, we need a 4-address, 3-bit addressable memory that allows us to write to each bit at a location separately. To do so, we hired a computer engineer from the University of Michigan.

The design is done by modifying the 4-address, 3-bit, memory that we discussed in class. Except for the WE input, all inputs and outputs remain the same. More specifically, ADDR is a 2-bit input for address selection, Din is a 3-bit input for providing bits when writing to a memory location.

As for the WE input, the modified memory structure no longer has a single WE input to all bits. Rather, when a location is selected, 3 WEout signals will independently determine if each bit in that location will be written. This modification has already been done by an Illinois student.

The Michigan engineer proposes to construct a combinational logic that provides a nice external interface for using the memory. The logic translates a 4-bit WE external input signal into the internal 3-bit WEout signals as follows:

WE is 4 bits wide and behaves as follows:

```

WE [3:0] = 0001

=>

write to bit 0 only

WE [3:0] = 0010

=>

write to bit 1 only

WE [3:0] = 0100

=>

write to bit 2 only

WE [3:0] = 1000

=>

write to all the bits

WE [3:0] = 0000

do not write to any of the bits

=>

WE [3:0] = other

treat as a read cycle

=>

```

**Part A** (6 points): For a first round of testing, we executed the six cycles shown on the left below. Assuming correct implementation and assuming that all the bits in the memory are initialized to 1, fill in the table on the right to reflect the final state of the memory (after the six cycles).

| Cycle # | ADDR[1:0] | WE[3:0] | Din[2:0] |

|---------|-----------|---------|----------|

| 1       | 00        | 0100    | 000      |

| 2       | 10        | 1000    | 010      |

| 3       | 10        | 0000    | 110      |

| 4       | 01        | 0010    | 001      |

| 5       | 11        | 0001    | 011      |

| 6       | 00        | 1000    | 100      |

| address | bit 2 | bit 1 | bit 0 |

|---------|-------|-------|-------|

| 00      |       |       |       |

| 01      |       |       |       |

| 10      |       |       |       |

| 11      |       |       |       |

4

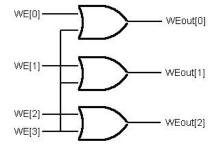

**Part B** (4 points): The memory designed by the Michigan alumnus passed the first test. However, the next round of tests revealed some undesired behavior. Examining his design, we found the following logic for generating the signals that specify whether or not each individual bit is written (WEout[2:0]).

In 25 words or less, explain the undesired behavior.

Name:

5

#### **Problem 4** (25 points): Finite State Machines

A certain finite state machine implements a pattern recognition system that recognizes specific sequences of inputs. Each input represents a letter, such as A or B. An input sequence can be written as a sequence of letters such as "ABAAABBABA...". For this finite state machine, the output Z is 1 when an input sequence has an even number of A's and an odd number of B's. Otherwise, the output Z is 0. The states needed are named as follows:

$\begin{array}{ll} S_{EE} & \text{even number of A's and even number of B's} \\ S_{EO} & \text{even number of A's and odd number of B's} \\ S_{OO} & \text{odd number of A's and odd number of B's} \\ S_{OE} & \text{odd number of A's and even number of B's} \end{array}$

**Part A** (8 points): Draw a high-level finite state machine transition diagram for the system. States and state names have been drawn for you. Add appropriate output values and all transition arcs. Label arcs as either A or B.

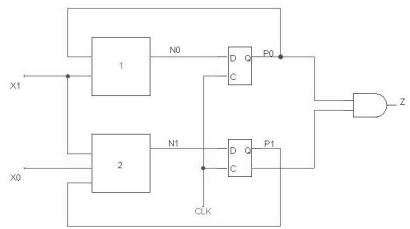

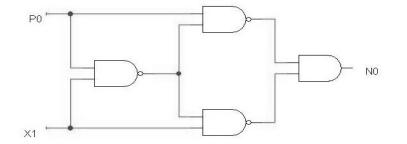

The circuit below shows an implementation of the finite state machine using two flip-flops and state representation (bits  $P_1P_0$ ) given by  $S_{EE}=00$ ,  $S_{EO}=01$ ,  $S_{OO}=10$ , and  $S_{OE}=11$ . The blocks labeled 1 and 2 use the current state  $P_1P_0$  and the inputs  $X_1X_0$  to calculate the next state,  $N_1N_0$ . The letter A is represented as  $X_1X_0=00$ , and the letter B is represented as  $X_1X_0=01$ .

Name:

### **Problem 4, continued:**

Part B (4 points): Based on the circuit below for Block 1, fill in the table for N0.

| <b>P0</b> | <b>X1</b> | N0 |

|-----------|-----------|----|

| 0         | 0         |    |

| 0         | 1         |    |

| 1         | 0         |    |

| 1         | 1         |    |

6

**Part C** (8 points): Based on your answer to **Part B** and on the truth table for **Block 2** (shown to the left below) fill in the next state table on the right for the FSM implementation. Note that input  $X_1X_0=11$  is not included in the table.

| <b>P1</b> | <b>X1</b> | $\mathbf{X0}$ | <b>N</b> 1 |

|-----------|-----------|---------------|------------|

| 0         | 0         | 0             | 1          |

| 0         | 0         | 1             | 0          |

| 0         | 1         | 0             | 0          |

| 0         | 1         | 1             | 1          |

| 1         | 0         | 0             | 0          |

| 1         | 0         | 1             | 1          |

| 1         | 1         | 0             | 1          |

| 1         | 1         | 1             | 0          |

| <b>P1</b> | <b>P0</b> | <b>X1</b> | X0 | N1 | N0 |

|-----------|-----------|-----------|----|----|----|

| 0         | 0         | 0         | 0  |    |    |

| 0         | 0         | 0         | 1  |    |    |

| 0         | 0         | 1         | 0  |    |    |

| 0         | 1         | 0         | 0  |    |    |

| 0         | 1         | 0         | 1  |    |    |

| 0         | 1         | 1         | 0  |    |    |

| 1         | 0         | 0         | 0  |    |    |

| 1         | 0         | 0         | 1  |    |    |

| 1         | 0         | 1         | 0  |    |    |

| 1         | 1         | 0         | 0  |    |    |

| 1         | 1         | 0         | 1  |    |    |

| 1         | 1         | 1         | 0  |    |    |

\*\*\*Part **D** (5 points): The input bits  $X_1X_0=10$  represent the letter C. Explain in one sentence how you can use the next state table from **Part C** to verify that the letter C is handled correctly by the FSM implementation.

| <b>Problem 5</b> (25 points): The von Neum                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ann Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| An LC-3 is about to perform an instruction The contents of the register file, PC, MAR, and part of memory are shown to the right.  You may wish to consult the last page of this eagives the LC-3 instruction set encoding and RT  Part A (8 points): On the lines below, for the next four instructions to be execut LC-3. For PC-relative addressing modes, write relative to PC rather than calculating the actuto be used, e.g., write "PC+x12" rather than a two values for that instruction. | FETCH.       R0       xA5A5       x3.         MDR, IR,       R1       x1000       x3.         R3       x1298       x3.         R3       x1981       x3.         ram, which       R4       x4345       x3.         L.       R6       x3A0F       x3.         write RTL       x3.       x4.       x4.         red by the addresses al address       MAR       x39A3       x3.         radding the       R7       x0E66       x3.         radding the       R7       x0E66       x3. | A06 x6CE A07 x1FF A08 x000 A09 x058 A0A x200 A0B x122 A0C x102 A0D x09F A10 x000 A11 x200 A12 x058 A13 x6CE |

| ${f Address}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\operatorname{RTL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                             |

| Part B (6 noints): Heing haved soined note                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ation, write the contents of the registers DO                                                                                                                                                                                                                                                                                                                                                                                                                                     | through D                                                                                                   |

| Part B (6 points): Using hexadecimal nota MAR, MDR and IR after the LC-3 processes R0 R1                                                                                                                                                                                                                                                                                                                                                                                                           | PC MAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | through R                                                                                                   |

| MAR, MDR and IR after the LC-3 processes                                                                                                                                                                                                                                                                                                                                                                                                                                                           | es the first three instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | through R                                                                                                   |

| R0 R1 R2 R3 R4 R5 R6 R7  Part C (4 points): Using hexadecimal no                                                                                                                                                                                                                                                                                                                                                                                                                                   | PC MAR MDR IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | and MDI                                                                                                     |

| R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PC MAR MDR IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | and MDI                                                                                                     |

| R0 R1 R2 R3 R4 R5 R6 R7  Part C (4 points): Using hexadecimal no the LC-3 processes one additional instruction a                                                                                                                                                                                                                                                                                                                                                                                   | The first three instructions.  PC MAR MDR IR  IR  Mattaion, write the contents of the PC, MAR fter Part B, i.e., four instructions in al MAR MDR  MDR  That is three instructions.                                                                                                                                                                                                                                                                                                | and MDI                                                                                                     |

| Name: | 8 |

|-------|---|

|       |   |

Use this page for scratchwork.

# NOTES: RTL corresponds to execution (after fetch!); JSRR not shown

| ADD 0001 DR SR1 0 00 SR2 AD                                                    | DD DR, SR1, SR2 LI  | .D [  | 0010 DR PCoffset9                                | LD DR, PCoffset9       |

|--------------------------------------------------------------------------------|---------------------|-------|--------------------------------------------------|------------------------|

| DR ← SR1 + SR2, Setcc                                                          |                     |       | $DR \leftarrow M[PC + SEXT(PCoffset9)], Setcc$   |                        |

| ADD 0001 DR SR1 1 imm5 AD                                                      | DD DR, SR1, imm5 LE | .DI [ | 1010 DR PCoffset9                                | LDI DR, PCoffset9      |

| DR ← SR1 + SEXT(imm5), Setcc                                                   |                     |       | $DR \leftarrow M[M[PC + SEXT(PCoffset9)]],Setcc$ |                        |

| AND 0101 DR SR1 0 00 SR2 A                                                     | ND DR, SR1, SR2 LD  | DR [  | 0110 DR BaseR offset6                            | LDR DR, BaseR, offset6 |

| DR ← SR1 AND SR2, Setcc                                                        |                     |       | $DR \leftarrow M[BaseR + SEXT(offset6)],Setcc$   |                        |

| AND 0101 DR SR1 1 imm5 A                                                       | ND DR, SR1, imm5 LE | EA [  | 1110 DR PCoffset9                                | LEA DR, PCoffset9      |

| $DR \leftarrow SR1 \; AND \; SEXT(imm5),  Setcc$                               |                     |       | DR ← PC + SEXT(PCoffset9), Setcc                 |                        |

|                                                                                | R{nzp} PCoffset9 NC | от [  | 1001 DR SR 111111                                | NOT DR, SR             |

| ((n AND N) OR (z AND Z) OR (p AND P)):<br>PC $\leftarrow$ PC + SEXT(PCoffset9) |                     |       | DR ← NOT SR, Setcc                               |                        |

| JMP 1100 000 BaseR 000000 JI                                                   | MP BaseR S          | вт [  | 0011 SR PCoffset9                                | ST SR, PCoffset9       |

| PC ← BaseR                                                                     |                     |       | $M[PC + SEXT(PCoffset9)] \leftarrow SR$          |                        |

| JSR 0100 1 PCoffset11 J                                                        | SR PCoffset11 S     | ті [  | 1011 SR PCoffset9                                | STI SR, PCoffset9      |

| $R7 \leftarrow PC, PC \leftarrow PC + SEXT(PCoffset11)$                        |                     |       | $M[M[PC + SEXT(PCoffset9)]] \leftarrow SR$       |                        |

| TRAP 1111 0000 trapvect8 T                                                     | RAP trapvect8 ST    | TR    | 0111 SR BaseR offset6                            | STR SR, BaseR, offset6 |

| $R7 \leftarrow PC, PC \leftarrow M[ZEXT(trapvect8)]$                           |                     |       | $M[BaseR + SEXT(offset6)] \leftarrow SR$         |                        |